生成对抗网络-【异质集成】高k复杂氧化物栅介质在GaN HEMTs上的异质集成

推荐 原创COMMUNICATIONS ENGINEERING | (2024) 3:15论文阅读。

文章讨论了高k复杂氧化物栅介质在宽带隙高电子迁移率晶体管(HEMTs)上的异质集成。

其核心内容的总结如下:

研究背景:

- 异质集成不同晶体材料因其在高性能多功能电子和光子器件中的潜力而受到关注。

- 传统的异质结构制造方法是通过异质外延,但在单晶生长不同材料时存在限制,这阻碍了在传统半导体平台上实现高质量异质结构的可能性。

研究内容:

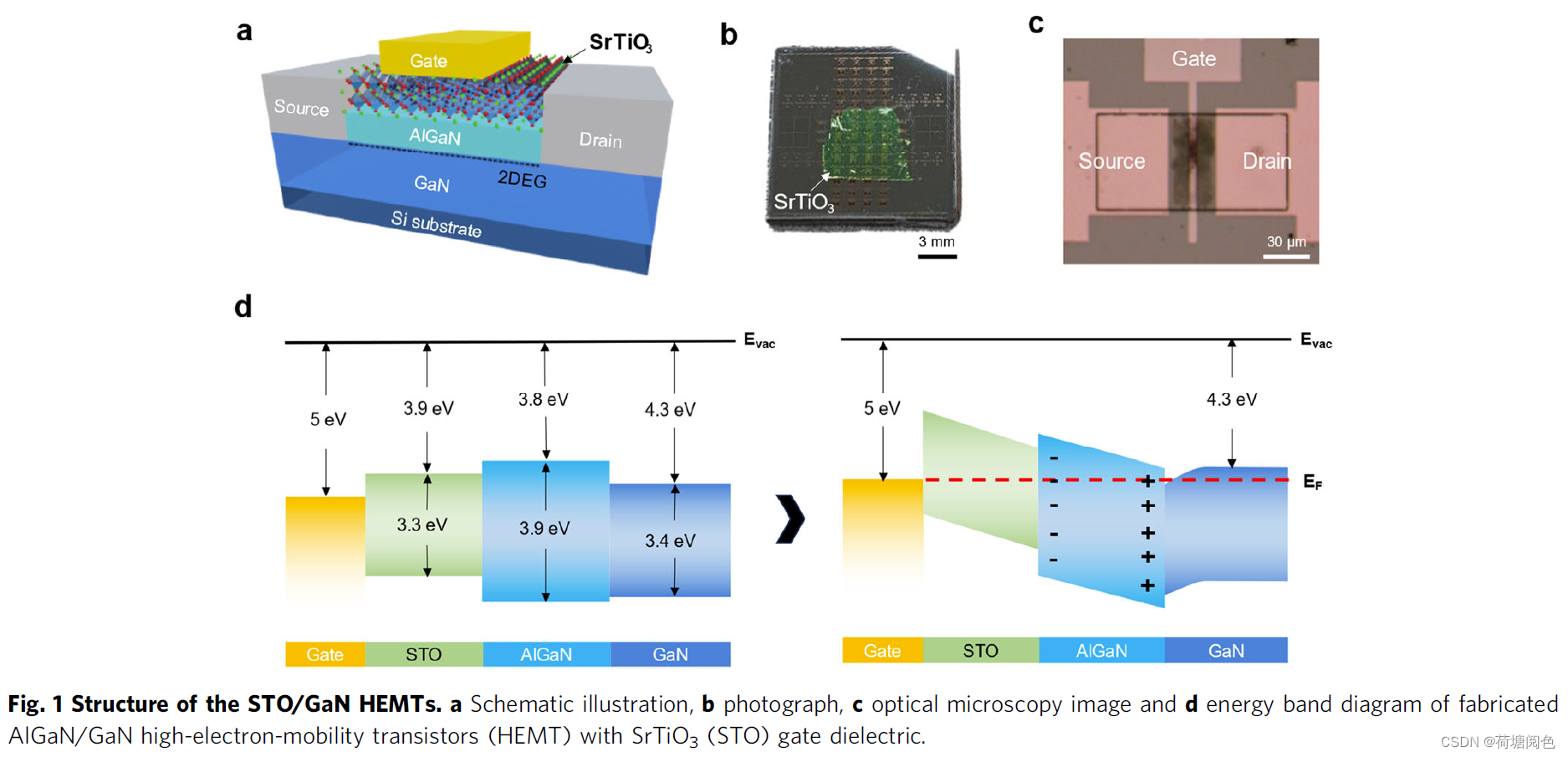

- 本研究展示了通过外延剥离和直接堆叠的异质集成方法,成功地将高κ复杂氧化物SrTiO3与GaN异质结构集成在一起,形成自由悬挂膜形式的栅氧化层。

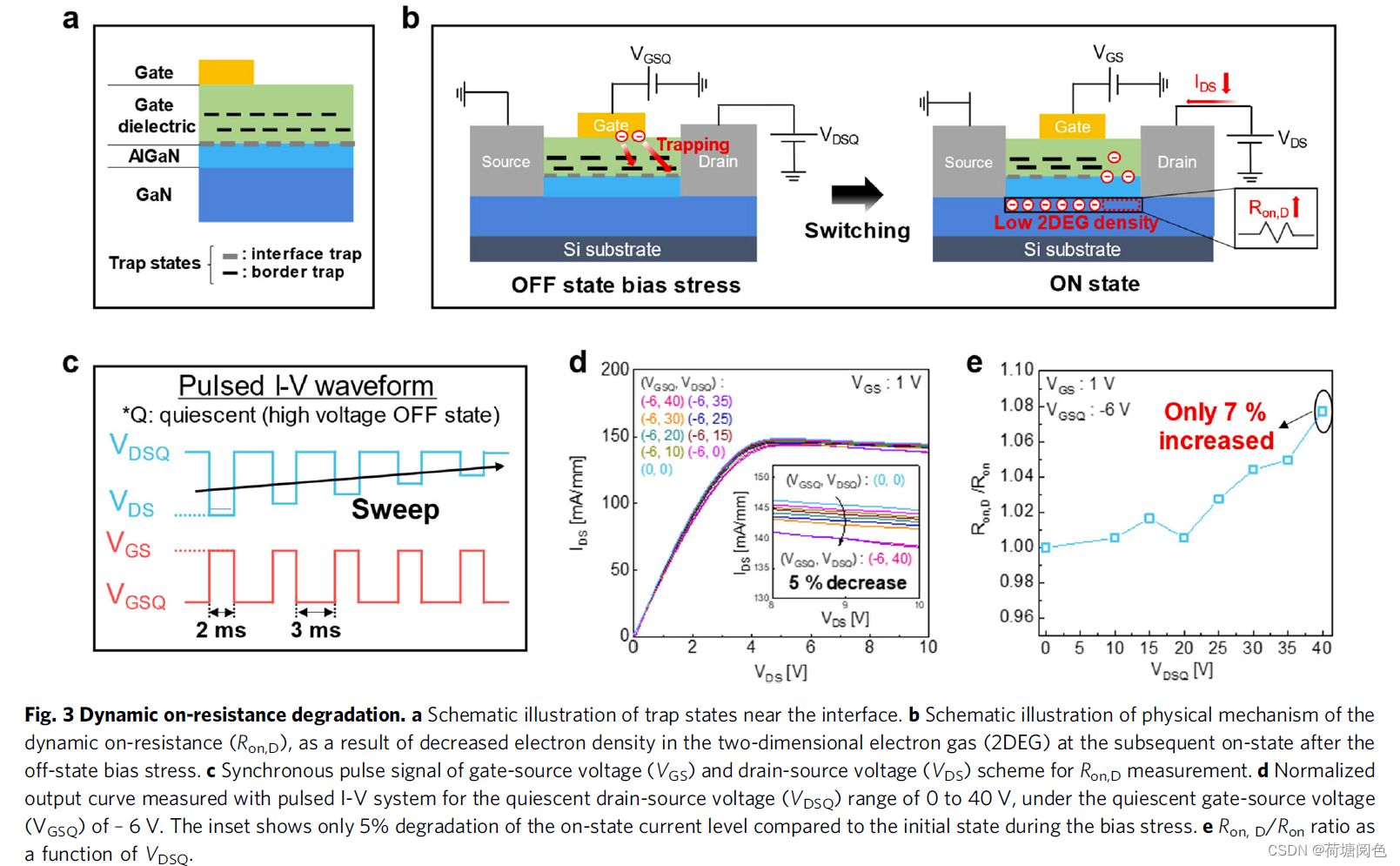

- 制造的器件显示出接近玻尔兹曼极限的陡峭次阈值摆动,以及可忽略的迟滞和低动态导通电阻,表明SrTiO3栅氧化层和GaN异质结构之间具有非常低的缺陷密度。

实验结果:

- 实验结果表明,通过直接材料堆叠的异质集成是制造传统外延无法实现的功能异质结构的有前途的途径。

- 研究中制造的GaN基HEMT具有优异的电气特性,如可忽略的迟滞(ΔV),接近玻尔兹曼极限的低次阈值摆动(SS),以及低动态导通电阻。

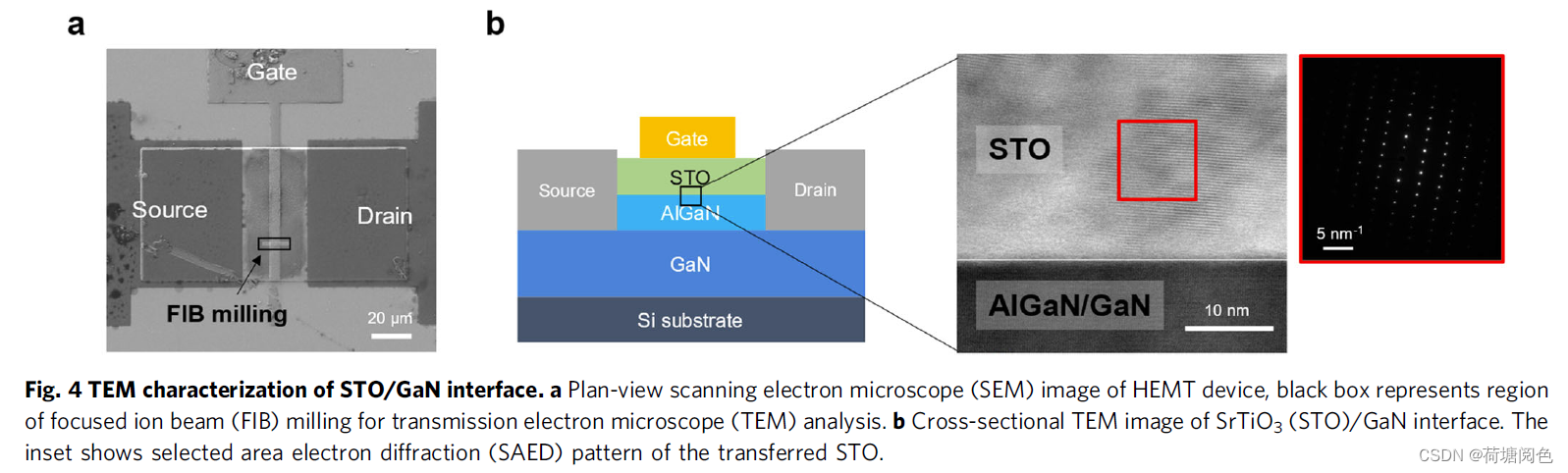

- 通过透射电子显微镜(TEM)直接观察STO/GaN界面,确认了STO膜转移后保持其晶体性质,并且STO/GaN界面之间不存在缺陷、气隙、意外界面层或残留物。

结论:

- 研究团队通过外延层转移方法在AlGaN/GaN HEMT上异质集成了晶体复杂氧化物材料作为栅介质。

- 使用具有超高κ特性的STO作为栅氧化层,制造了MOS-HEMT器件。

- 制造的器件在1 µA/mm的漏电流下显示出可忽略的迟滞(ΔV),并且最小SS值为62 mV dec−1。

- 动态导通电阻测量进一步分析了界面质量,其中器件的最大电阻增加仅为7%。

- 通过TEM确认STO/GaN之间不存在不需要的界面层、残留物或气隙,并且转移的STO保持其晶体性质。

方法:

- 材料准备和器件制造:使用金属有机化学气相沉积(MOCVD)在Si(111)衬底上生长GaN HEMT。

- 电气和材料特性表征:使用半导体参数分析仪测量制造器件的电气特性,并使用扫描电子显微镜(SEM)、聚焦离子束(FIB)和透射电子显微镜(TEM)进行结构和界面分析。

更多【生成对抗网络-【异质集成】高k复杂氧化物栅介质在GaN HEMTs上的异质集成】相关视频教程:www.yxfzedu.com

相关文章推荐

- stm32-FPGA与STM32_FSMC总线通信实验 - 其他

- spring-springboot集成redis -- spring-boot-starter-data-redis - 其他

- ios-LibXL 4.2.0 for c++/net/win/mac/ios Crack - 其他

- unity-Unity DOTS系列之System中如何使用SystemAPI.Query迭代数据 - 其他

- 网络-openssl+SM2开发实例一(含源码) - 其他

- spring-Redis的内存淘汰策略分析 - 其他

- 单一职责原则-01.单一职责原则 - 其他

- 分布式-Java架构师分布式搜索词库解决方案 - 其他

- 电脑-京东数据分析:2023年9月京东笔记本电脑行业品牌销售排行榜 - 其他

- 云计算-什么叫做云计算? - 其他

- 编程技术-基于springboot+vue的校园闲置物品交易系统 - 其他

- 零售-OLED透明屏在智慧零售场景的应用 - 其他

- 交互-顶板事故防治vr实景交互体验提高操作人员安全防护技能水平 - 其他

- unity-原型制作神器ProtoPie的使用&Unity与网页跨端交互 - 其他

- python-Django知识点 - 其他

- 前端-js实现定时刷新,并设置定时器上限 - 其他

- 需求分析-2023-11-11 事业-代号s-duck-官网首页需求分析 - 其他

- node.js-【第2章 Node.js基础】2.5 Node.js 的定时器 - 其他

- 编程技术-parasoft Jtest 使用教程:防止和检查内存问题 - 其他

- hive-【Python大数据笔记_day06_Hive】 - 其他

记录自己的技术轨迹

文章规则:

1):文章标题请尽量与文章内容相符

2):严禁色情、血腥、暴力

3):严禁发布任何形式的广告贴

4):严禁发表关于中国的政治类话题

5):严格遵守中国互联网法律法规

6):有侵权,疑问可发邮件至service@yxfzedu.com

近期原创 更多