fpga开发-用户数据的FLASH存储与应用(FPGA架构)

推荐 原创该系列为神经网络硬件加速器应用中涉及的模块接口部分,随手记录,以免时间久了遗忘。

一 背景

我们知道,在FPGA做神经网络应用加速时,涉及到权重参数的存储和加载。通常在推理过程中,会将权重参数存储在外部DDR或片上SRAM上。但是对于一些大的网络模型,往往片上RAM受限而无法完全保存权重,因此需要将权重放置在外部DDR或者PSRAM等外部存储器中,等具体需要的时候,从片外load进片上,然后计算完丢弃,重新load下一批次权重。

这里就涉及到,当我们的应用固化后,片外DDR存储器权重加载问题,通常包括集中方法,一是上电后,通过PCIE/UART/SD卡等load进DDR;另一种方法是将权重和FPGA bit文件一并打包存储在FLASH中,上电后,从FLASH中加载至片外DDR,或者直接load进片上SRAM。

为了简化设计,这里采用第二种方法,将FPGA位流和权重等用户数据打包存入Flash配置芯片中。

二 方案设计

FPGA:XC7A50T

配置芯片:MX25L6433F Flash

为了简化设计,这里采用第二种方法,将FPGA位流和权重等用户数据打包存入Flash配置芯片中。

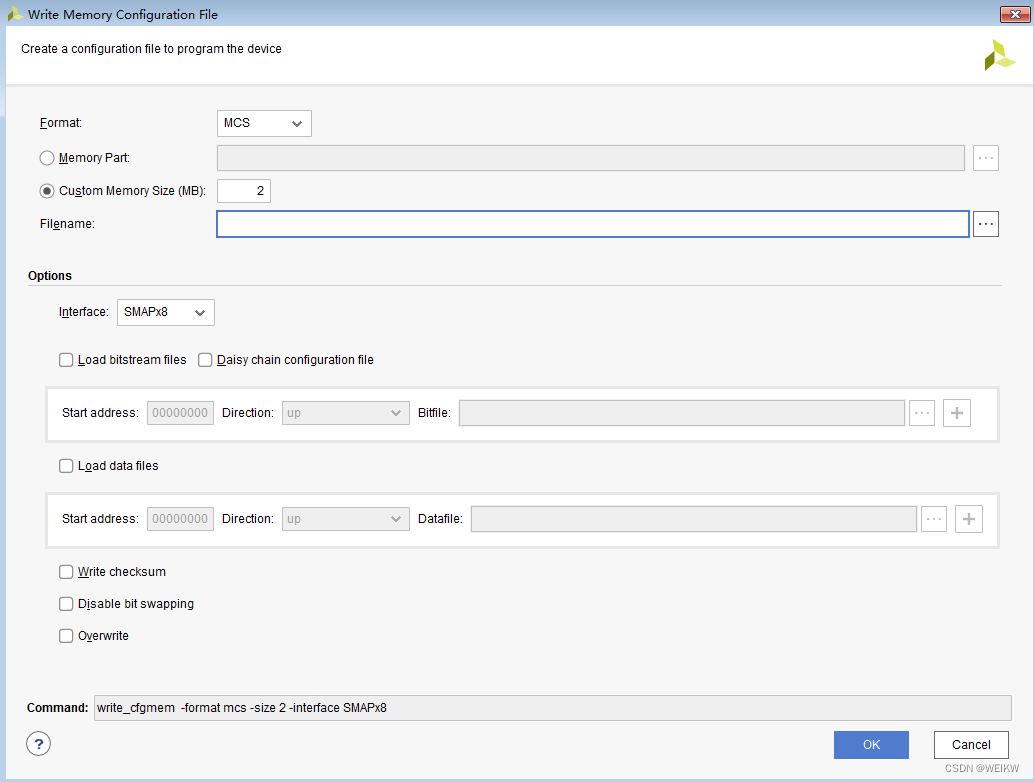

简单讲就是通过VIVADO的工具,将用户数据和FPGA bit进行打包生成mcs,同时注意需要将用户数据存储在程序空间之外。上电后,通过SPI_Loader将Flash中的用户数据,加载至外部DDR即可。

架构分析:

架构分析:

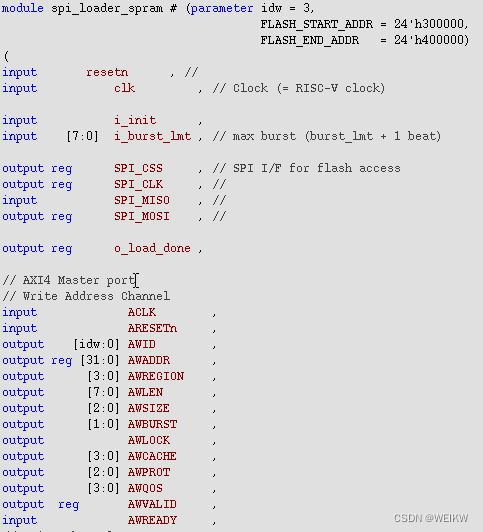

SPI接口部分,没有什么新意,和常规读写FLASH一样,用户接口为了方便,直接采用AXI协议进行控制,方便与标准总线互通。

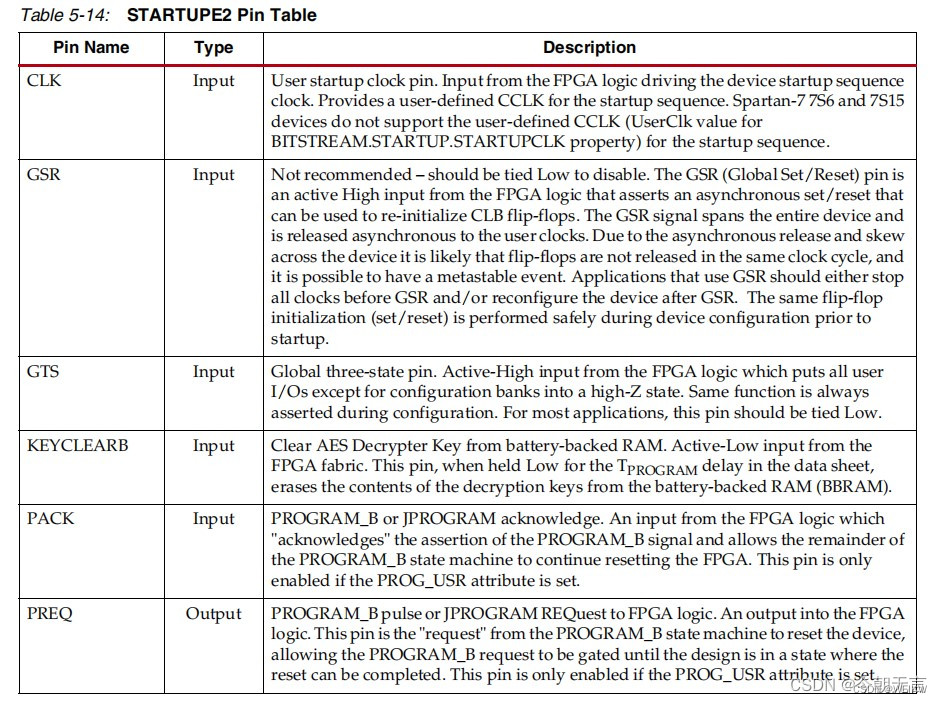

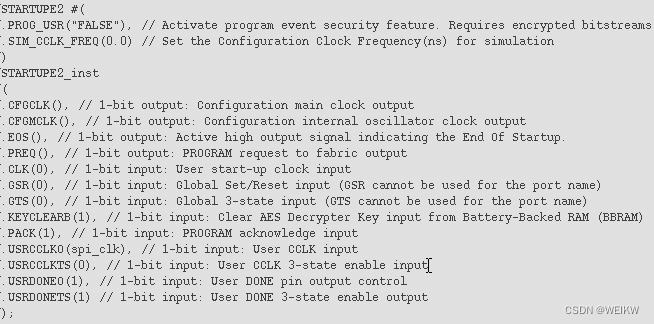

另外,由于涉及对FLASH读控制操作,需要配置FLASH管脚,需要调用STARTUPE2原语,用于对CCLK进行设置,用于该时钟。

调用方法:

调用方法:

更多【fpga开发-用户数据的FLASH存储与应用(FPGA架构)】相关视频教程:www.yxfzedu.com

相关文章推荐

- 编程技术-任意注册漏洞 - 其他

- 安全-赛宁网安入选国家工业信息安全漏洞库(CICSVD)2023年度技术组成员单 - 其他

- jvm-深入理解JVM虚拟机第二十四篇:详解JVM当中的动态链接和常量池的作用 - 其他

- 编程技术-ROS 通信机制 - 其他

- 聚类-无监督学习的集成方法:相似性矩阵的聚类 - 其他

- layui-layui 表格(table)合计 取整数 - 其他

- 编程技术-rt-hwwb前端面试题 - 其他

- node.js-Vite和Webpack区别 - 其他

- python-python用pychart库,实现将经纬度信息在地图上显示 - 其他

- node.js-Electron-vue出现GET http://localhost:9080/__webpack_hmr net::ERR_ABORTED解决方案 - 其他

- web安全-APT攻击的特点及含义 - 其他

- 51单片机-51单片机应用从零开始(二) - 其他

- objective-c-【Objective-C】Objective-C汇总 - 其他

- 云原生-SpringCloud微服务:Eureka - 其他

- react.js-react+星火大模型,构建上下文ai问答页面(可扩展) - 其他

- node.js-taro(踩坑) npm run dev:weapp 微信小程序开发者工具预览报错 - 其他

- 云原生-Paas-云原生-容器-编排-持续部署 - 其他

- 网络-漏洞扫描工具的编写 - 其他

- 组合模式-二十三种设计模式全面解析-组合模式与迭代器模式的结合应用:构建灵活可扩展的对象结构 - 其他

- java-【Proteus仿真】【51单片机】多路温度控制系统 - 其他

2):严禁色情、血腥、暴力

3):严禁发布任何形式的广告贴

4):严禁发表关于中国的政治类话题

5):严格遵守中国互联网法律法规

6):有侵权,疑问可发邮件至service@yxfzedu.com