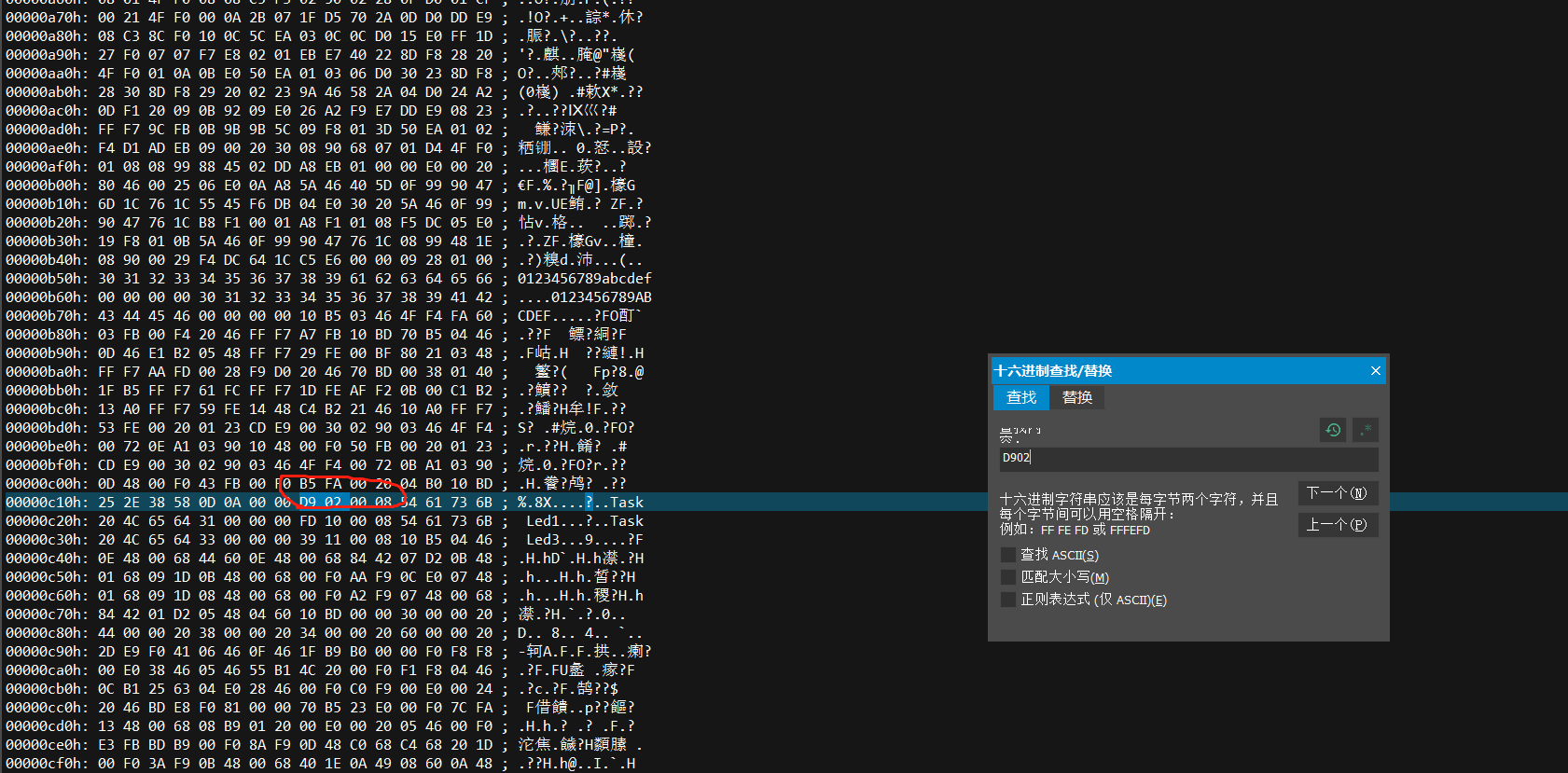

智能设备-关于thumb2指令下函数运行地址对齐问题及验证固件分析

推荐 原创更多【关于thumb2指令下函数运行地址对齐问题及验证固件分析】相关视频教程:www.yxfzedu.com

相关文章推荐

- D3CTF2023 REVERSE - CTF对抗

- IL2CPP 逆向初探 - CTF对抗

- 利用Powershell击败.NET恶意样本 - 软件逆向

- CLFS信息泄露漏洞CVE-2023-28266分析 - 软件逆向

- 新型Windows内核池风水利用工具研究 - 软件逆向

- Frida-Core 源代码速通笔记 - 软件逆向

- 派拉软件连续入选Gartner《身份治理与管理市场指南》全球代表厂商 - 企业安全

- 黑客恶意重打包Chrome 通过“软件盒子”、“海量软件管家”等传播 - 企业安全

- 安卓逆向基础知识之Java与smali基础 - Android安全

- FridaLocalManager 本地持久化群控管理工具 - Android安全

- Hex Comparison注册分析 - 软件逆向

- Windows远程相关 - 软件逆向

- 揭秘360加固保核心安全能力——应用运行时自保护能力(RASP) - 企业安全

- 未导出函数PspTerminateProcess关闭360 - 软件逆向

- 记录闯关游戏第八关WinXor题解记录 - CTF对抗

- 入门编译原理之前端对接LLVM IR - 软件逆向

- KCTF2023第二题 CN星际基地 - CTF对抗

- KCTF2023 第二题wp - CTF对抗

- 利用Magisk将Charles证书写入系统列表 - Android安全

- 入门编译原理之LLVM IR转汇编代码 - 软件逆向

记录自己的技术轨迹

文章规则:

1):文章标题请尽量与文章内容相符

2):严禁色情、血腥、暴力

3):严禁发布任何形式的广告贴

4):严禁发表关于中国的政治类话题

5):严格遵守中国互联网法律法规

6):有侵权,疑问可发邮件至service@yxfzedu.com

近期原创 更多

- 算法-03 矩阵与线性变换

- android-Android Studio(控件常用属性)

- 编程技术-ES使用ik分词器查看分词结果及自定义词汇

- asp.net-asp.net水资源检测系统VS开发sqlserver数据库web结构c#编程Microsoft Visual Studio

- 编程技术-jQuery中遍历元素each

- 编程技术-rabbitmq下载安装教程

- 编程技术-Codeforces Round 908

- 编程技术-Leetcode543. 二叉树的直径

- 机器学习-IBM Qiskit量子机器学习速成(一)

- 编程技术-3D模型格式转换工具HOOPS Exchange如何获取模型的特征树?